QT1230 4通道5Gsps/1.25Gsps CPCI FPGA开放的采集卡

规格

大支持4通道同步采集。

高5GSPS采样率/单通道、2.5GSPS采样率/2通道、1.25GSPS采样率/4通道。

时间交错自适应校准系统。

10bit 转换精度。

支持AC、DC藕合方式;支持高频脉冲信号输入。

大板载2GB DDR3存储器。

支持外部触发输入或输出,;支持用户扩展IO。

支持GPS同步和时间戳功能。

标准6U CPCI结构,支持PCI 32bit 33MHz传输总线。

FPGA支持用户自定义逻辑开发。

应用

宽带雷达系统

激光雷达系统

宽带通信系统

高能物理测试

光电倍增管采集系统

软件支持

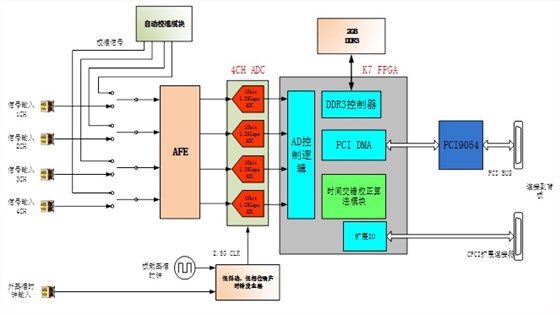

系统框图:

硬件功能以及选项:

高速ADC采集模式

QT4512采集模块单片集成4个10bit 1.25Gsps 高速ADC,具有输入方式灵活和通道一致性好特点。当工作在4通道模式时,采样率为每通道1.25Gsps;工作在2通道模式时,采样率为毎通道2.5Gsps;工作在单通道模式时,采样率为5Gsps。

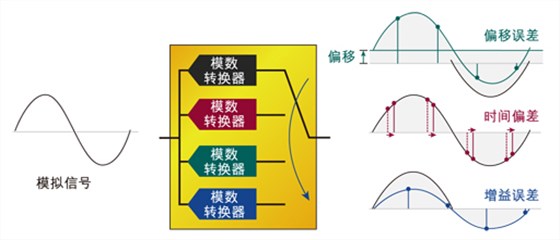

时间交错采集校准

当QT4512工作在2.5Gsps或5Gsps工作模式下时,采用2个或4个1.25Gsps ADC通过时间交错采集方法进行采集。由于模拟器件制造工艺不完善、电路寄生效应以及噪声等问题,造成不同ADC个体之间存在的差异。这些差异会在时间交错采集系统中引起增益失配(Gain Mismatch)、偏置失配(Offset Mismatch)以及时钟失配(Clock Timing Mismatch),使得采样数据中存在失配误差,这个误差能够显著的引入采样噪声和非线性失真,使得采样的SNR和SFDR达不到单个ADC所能达到的性能。

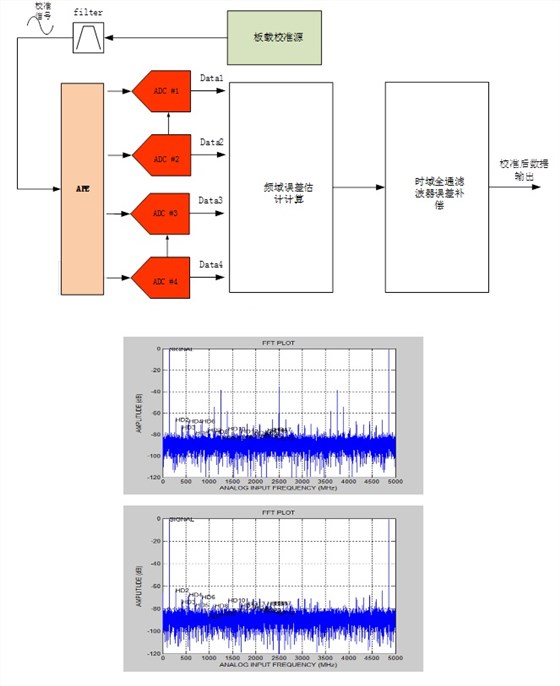

坤驰科技开发的时间交错采样校准算法能持续提供模数转换器的增益、偏移和时间偏差误差的后台估计值,同时校准估计误差,对全部失配误差重新构建。误差校正算法对于任何输入信号类型,以及静态和动态失配误差很有效。

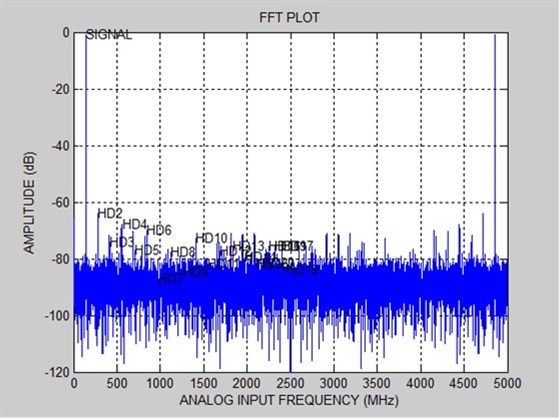

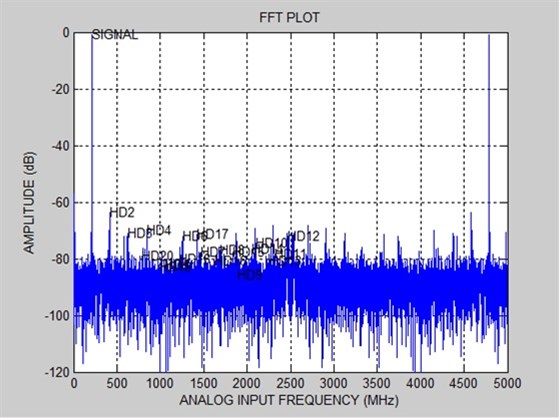

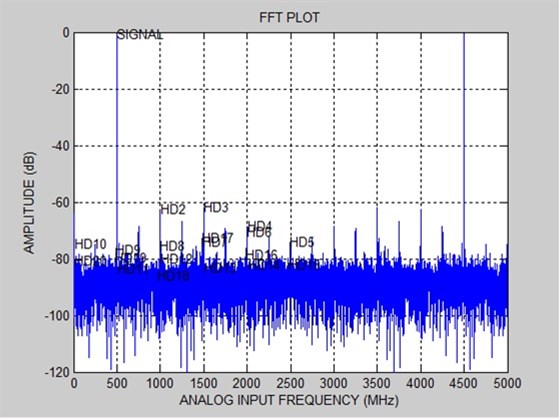

输入频率140MHz的正弦波在5GHz采样率下误差校正前后频域效果对比

(上图为校正前,下图为校正后)

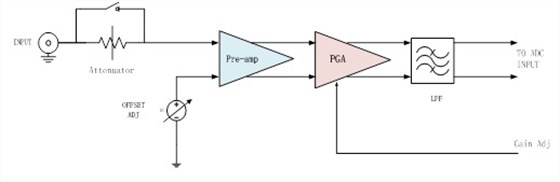

模拟信号输入

QT4512具有4个独立的模拟信号输入通道为用户提供4种输入方式选择:

-OPT1: 交流耦合

采用Balun耦合,单端输入

输入阻抗50Ω,输入范围500mVpp

默认输入带宽4.5MHz~2GHz

-OPT2: 直流耦合

采用运算放大器直流耦合,单端输入

输入阻抗50Ω,输入范围1Vpp,可配置板载衰减器

默认输入带宽DC~1GHz,可配置板载滤波器

-OPT3: 带程控增益输入

交流、直流耦合,单端输入

支持软件程控增益设置,调节范围-20dB~+20dB

输入阻抗50Ω,输入范围±50mVpp到±5Vpp,软件可配置

输入带宽DC~1GHz

具有直流偏置调节功能

-OPT4: 用户定制输入带宽

交流/直流耦合可选

增益范围可选

输入阻抗50Ω/1MΩ可选

输入带宽直流DC~2GHz,交流600K~3GHz可选

板载采集存储器

QT4512板载64位宽DDR3存储器用于缓存采集数据。DDR3读写数据率为1667MHz,能为用户提供大100Gb/s的数据吞吐率,支持各种采集模式下的数据并发读写。

板载内存容量选项:

-OPT5: 1GB(总共512Msample,4通道同时工作时 125Msample/每通道)

-OPT6: 2GB(总共1Gsample,4通道同时工作时 250Msample/每通道)

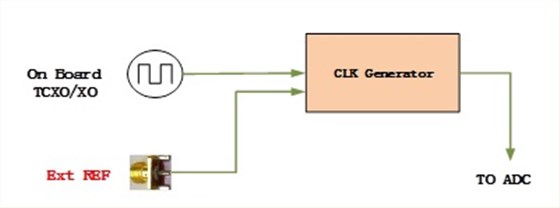

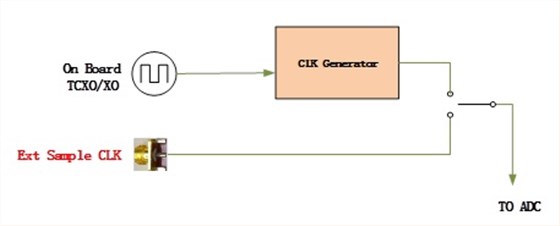

采集时钟发生器

采集时钟的随机抖动会劣化采集系统的信噪比,而且随着输入信号频率的增加,采集时钟的抖动对信噪比的影响会越来越明显。因此QT4512采用超低抖动时钟信号产生模块配合高稳定、低相位噪声时钟参考源来保证采集时钟的性能。

时钟发生器采用独立的屏蔽模块,支持板载参考源、外部参考时钟源以及同步接口参考时钟输入。

时钟模块选项:

-OPT7: 板载超低相噪TCXO参考源

100MHz

相位噪声 -157dBc/Hz AT 10KHz;-168dBc/Hz AT floor

温度稳定性: ±20ppm 0℃到70℃。

-OPT8: 板载超低相噪恒温晶体参考源

100MHz

相位噪声 -168dBc/Hz AT 10KHz;-180dBc/Hz AT floor

温度稳定性: ±0.05ppm 0℃到70℃。

-OPT9: 外参考输入

-OPT10: 外采集时钟输入

通用输入输出接口

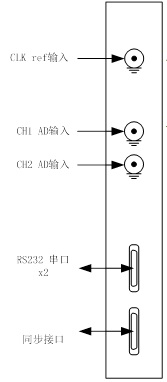

前面板 IO

前面板有RS232串口和4个通用IO可以使用。用户可以通过编程自定义这些IO的用途;同时这些IO通过软件设置,可作为输入、输出触发信号使用。

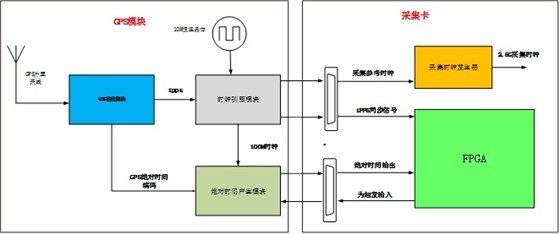

GPS同步和时间戳:

GPS同步模块由以下部分组成:

GPS接收模块:输出1pps秒脉冲,建议精度30ns rms(1σ)。

本机恒温晶体:输出10MHz,建议频率稳定度1e-9(阿伦方差)。

时钟驯服模块:根据GPS输出的1pps信号,同步每个采集模块的本地恒温晶体;同时产生1s频率的同步时钟信号。保障在GPS卫星短时间失锁情况下仍然能维持同步稳定。

GPS绝对时间模块:读取GPS授时时间,同时使用同步的100M时钟进行计数,产生本地20ns精度的绝对时间。

采集间模块同步机制:

同步原理如下图所示:

同步机制在采集模块内采用两种方式实现同步:

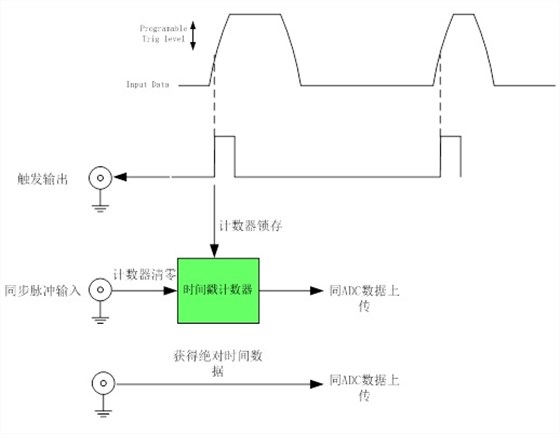

时间戳模式: 驱动时钟为采集时钟,频率2.5GHz,FPGA 5分频处理,分辨率为2ns。当有触发事件时,锁存时间戳计数器,将该计数器值同ADC数据值上传服务器。GPS同步模块输出的同步脉冲负责每秒为计数器清除一次,保证各个采集模块的计数器同步。如果各个采集模块是同时满足触发条件的,此时各个通道的计数器值应该相等。

绝对时间记录模式:触发脉冲输出到GPS绝对时间计数器中;当绝对时间计数器检测到上升沿,锁定绝对时间计数器,然后通过总线形式读取当前时间,同ADC采集数据上传主机。

采集功能以及选项:

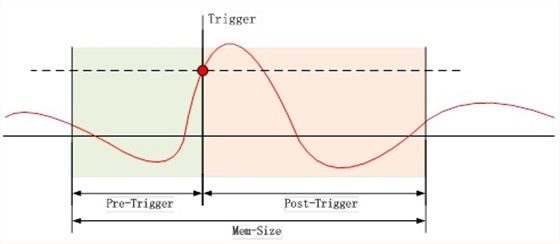

环形缓冲采集模式

QT4512设计了环形缓冲功能,因此具备采集触发时间前数据的能力。一旦采集卡满足触发条件,触发前的采集数据和触发后的数据同时存入板载的大容量存储器中;随后通过PCI Express总线读入到主机中。在一次触发-采集过程中,用户可以自由设置触发前采集数据长度和触发后采集数据长度,这两个长度之和为一次采集数据总长度。

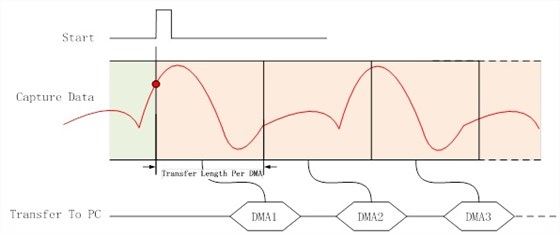

FIFO采集模式

该功能将板载内存虚拟为一个大容量FIFO,允许采集数据由该FIFO缓冲后连续不断的通过PCI Express 总线传输到主机内存或硬盘中。在FIFO模式下,系统会预先设置FIFO容量和实时监测FIFO状态,并自动启动PCI Express DMA操作,进行数据搬运工作。FIFO模式工作后,其采集数据长度容许无限长,限制条件为主机的内存容量或硬盘容量。

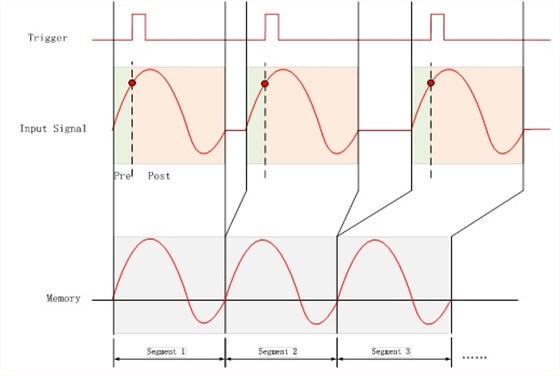

多次触发采集模式

多次触发采集模式将存储空间分成N个子段,可以接收连续触发操作。系统自动将每次触发前后采集的数据存入对应的存储器子段,这个过程不需要软件干预,采集卡也不需要重新启动。存储空间分段的数量受设置的每次采集数据长度和板载内存容量大小限制;FIFO模式下分段数量不受限制。

触发模式

QT4512支持多种触发模式:

软件触发

通道触发,任意4个通道均能设置为触发源,触发方式有上升沿大于、下降沿小于阈值触发;阈值窗口触发。

外触发,前面板上的4个通用IO均能作为触发源使用,可上沿或下沿触发或各个IO组合逻辑触发。

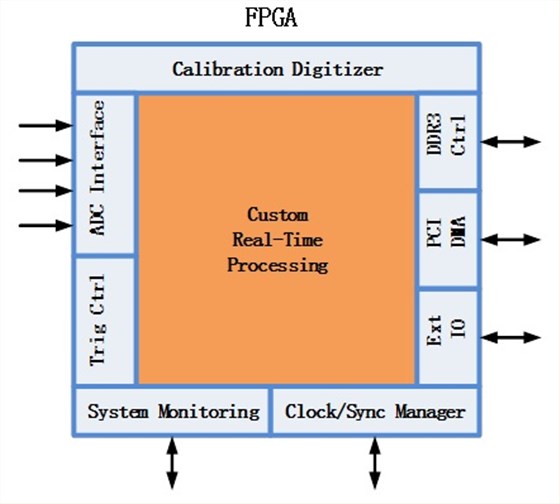

用户FPGA开发包 -OPT11:

QT4512支持用户自定义逻辑开发。我们提供完整的FPGA逻辑工程,并提供基于Verilog-HDL编写的用户逻辑接口源代码。FPGA开发软件使用XILINX ISE 14.5。

同时开放FPGA JTAG 调试接口。用户可以使用XILINX USB-JTAG电缆和ChipScope 软件进行逻辑在线调试。

FPGA 开发包选项:

-OPT12:采用XC7K325T-2 FPGA

-OPT13:采用XC7K410T-2 FPGA

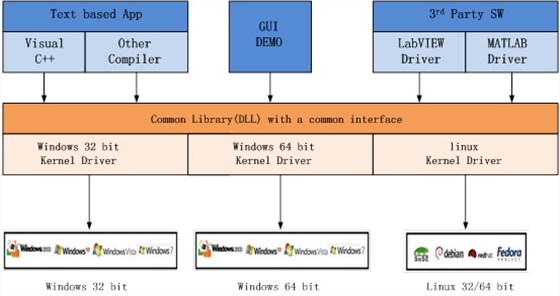

软件以及选项

Windows 设备驱动

QT4512提供32位Windows XP、Windows 7以及64位windows 7设备驱动程序。可以使用Visual C++, Visual Studio 2010,LabWindows/CVI开发。

Linux 设备驱动

QT4512支持32位和64位内核的linux系统:RedHat、Fedora、Ubuntu或Debian。Linux 驱动程序完全支持GNU C++编译器。

QTCapture Lab

QTCapture Lab应用软件基于Windows 32位/64位平台,具有虚拟示波器功能,方便设置硬件,读取/保存数据以及波形显示/频谱分析功能。

其功能和界面如下所示:

第三方软件支持

QT4512提供LabView,LabWidows/CVI以及MATLAB程序接口。以上程序均提供例程。

技术规格参数

动态技术指标

噪声和失真

Fs=5GspsFin=140MHz

Fs=5Gsps Fin=210MHz

Fs=5GspsFin=500MHz

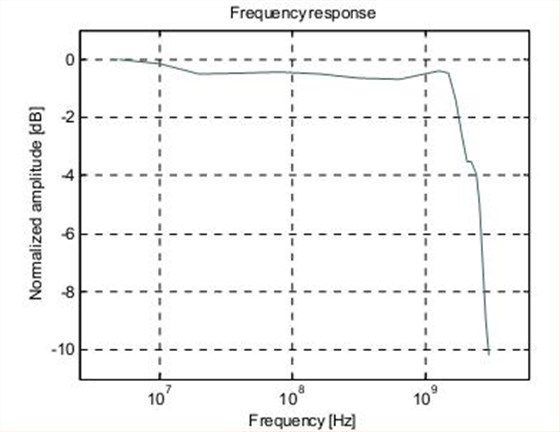

输入带宽

采集时钟抖动:

订货信息

扫微信二维码随时了解坤驰动态

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰